Das Interconnection Board

Der zentrale Baustein der gesamten Steuerung

Für das Herzstücks der gesamten Steuerung, dem Interconnection-Board, steht wie vorher beschrieben die Realisierung mittels TTL-Bausteinen fest. Ebenso steht fest, dass die 220-V-Lasten mit Tastern ein- und ausgeschaltet werden. Es braucht also … ein FlipFlop (FF). Von den verschiedenen Typen FlipFlop (RS-, JK-, D- und T-FF) fällt die Wahl auf das T-FF (Toggle-FF), denn es soll mit nur einem Taster geschaltet werden (t = toggle, engl. für hin- und herschalten).

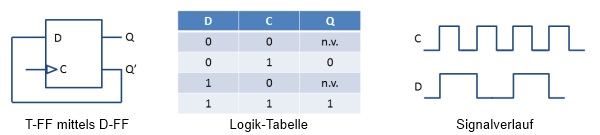

Das T-FF wird mit einem D-FF realisiert, das folgende Bild zeigt das grundsätzliche Schaltschema und das Symbol des D-FF:

Das T-FF entsteht nun durch Rückführung des negierten Ausgangs Q‘ auf den Eingang D. Wann immer sich auf dem Takteingang C das Signal von 0 auf 1 ändert, wird der Zustand des Dateneingang D an Q übernommen, bei C = 0 ändert sich nichts (n.v.). So erhält man ein Einflanken-gesteuertes D-FF, und dies zeigen Logik-Tabelle und Signalverlaufs-Schema sehr gut. Im Grunde genommen ist das das Prinzip eines Frequenzteilers. Ein grosser Vorteil des T-FF ist auch, dass sein Zustand jederzeit stabil ist, der verbotene Zustand Q = Q‘ kann aufgrund der Signalrückführung nicht existieren:

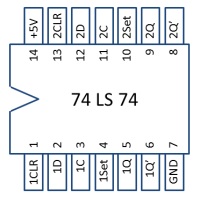

Das hier zum Einsatz kommende IC ist das 74LS74. Das folgende Bild zeigt dessen Belegungsplan. Man erkennt auch die zusätzlichen Anschlüsse Set und CLR. In unserer Schaltung wird CLR verwendet, um mit einem einzigen Taster alle Schaltkanäle zu löschen, sprich, mit einem Taster alle Geräte auszuschalten:

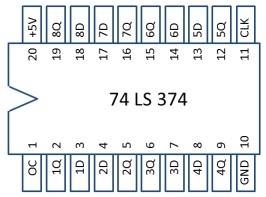

Für das Interconnection-Board stehen jetzt bereits drei Funktions-Einheiten fest: der Taster, das FlipFlop und die Entprellstufe für den Taster. Werfen wir einen Blick auf die Entprellstufe. Um das Schwingen der Schaltkontakte zu eliminieren und einen einzigen Schaltimpuls zu erhalten, wird klassisch z.B. ein RS-FlipFlop hinter den Taster geschaltet. Dafür braucht es einen Taster-Umschalter und 2 Pull-up Widerstände je Taster. Diesen aufwändigen Weg wollte ich nicht gehen, aber das FlipFlop Prinzip bleibt bei der hier vorgestellten Lösung erhalten. Für die Entprellung verwenden wir das IC 74LS374, dass aus 8 FlipFlops und einem CLK Eingang besteht. Das Bild zeigt dies:

Wenn sich am Takteingang CLK das Signal von 0 auf 1 ändert, wird Q(n) = D(n), also das Signal an den FlipFlop-Eingängen auf den Ausgang durchgeschaltet. Die Frage ist hier allenfalls, wann der Takt zu erfolgen hat, denn das IC erhält keine Information darüber, wann ein Taster betätigt wurde.

Der Trick besteht darin, den Takt zyklisch zu ändern, also periodisch einen 0-1-Sprung durchzuführen,

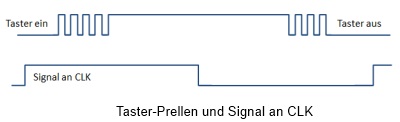

und diese Periode deutlich länger zu machen als die typischen Taster-Prellzeiten. Für letztere gelten Werte von ein paar 100 µs bis zu einigen 10 Millisekunden. Erfolgt der 0-1-Sprung mit z.B. 300ms, so kann das Prellen keinen Einfluss mehr haben. Dies ist logisch, weil sich die Ausgangswerte nur bei Änderung von Low auf High am Takteingang ändern, und 2 Taktsignal-Änderungen weit ausserhalb der Prellzeiten liegen. Das nachstehende Bild verdeutlicht das (schematisch, nicht proportional).:

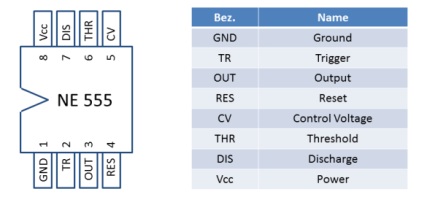

Den Takt gibt hier eine Schaltung mit dem Timer IC NE555 vor. Dieser weithin bekannte Baustein muss nicht weiter vorgestellt werden, das folgende Bild zeigt sein Anschluss-Schema:

Ein weiterer wichtiger Baustein unserer Schaltung ist der 74LS240, ein achtfach Puffer und Treiber-IC. Dieses wird zwischen den Tastern und den Entprell-FlipFlops geschaltet und dient dazu, dass sich durch etwaige längere Kabel zwischen den Tastern und dem Interconnection-Board abschwächende Signal zu verstärken. Den Baustein zeigt das folgende Bild:

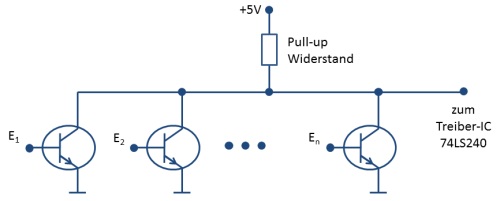

Ausserdem – und das war eines der Prämissen – können an den Treiber-Eingängen viele verschiedene Eingabe-Elemente parallel geschaltet und damit zusammengefasst werden. Die Voraussetzung dafür sind Open-Collector-Ausgänge auf den Boards, die das Schaltsignal liefern. In unserem Fall kommen neben den Tastersignalen auch Schaltbefehlt von Funkbausteinen sowie vom PC-Interface. Das folgende Bild zeigt das Open-Collector-Schaltprinzip:

Sind alle Transistoren gesperrt, zieht der Pull-up-Widerstand den Eingang auf Signal 1. Schaltet jedoch eines der Transistoren durch Signalspannung an den Eingängen E(1) bis E(n), so geht die gesamte Leitung auf logisch 0 und stellt dem Treiber-IC so dieses Signal zur Verfügung.

Der 74LS240 verfügt zusätzlich über einen Eingang G, der bei H-Signal den Baustein in den Tristate versetzt, und damit alle Eingänge sperrt. Dies könnte nützlich sein, will man z.B. seine Schalttafel vor unerlaubter Nutzung sperren.

Für den Abschluss des Interconnection-Boards braucht es dann nur noch ein weiteres Treiber-IC, an den die Lastrelais direkt angeschlossen werden können. Das hier eingesetzte IC ist das ULN2803, mit dessen NPN Darlington Transistoren genügend hoher Ausgangsstrom zur Verfügung steht, um die entfernten Lastrelais schalten zu können. Hier stehen wieder 8 Kanäle zur Verfügung, wie im Bild erkennbar:

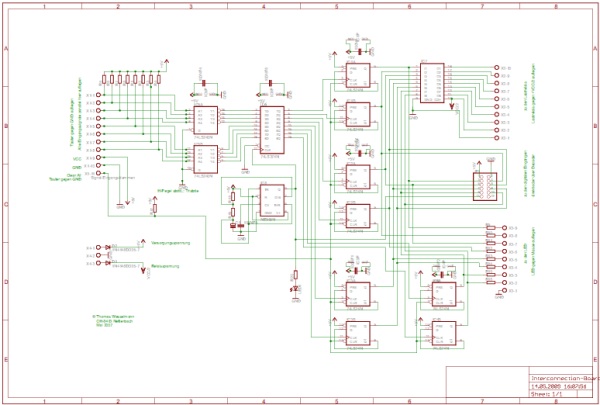

Damit ist das Herzstück der Steuerung fertig beschrieben. Das folgende Bild zeigt den kompletten Schaltplan. Neben den beschriebenen Elementen sind zusätzlich die Ausgänge für die LEDs auf dem Schaltpult und für die Eingänge des PC-Interface-Boards zu erkennen. Ebenso sieht man nun deutlich, was unterschwellig bereits mehrfach erwähnt wurde – das Interconnection-Board ist auf 8 Kanäle ausgelegt:

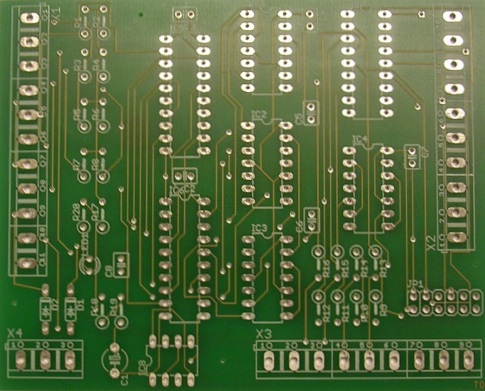

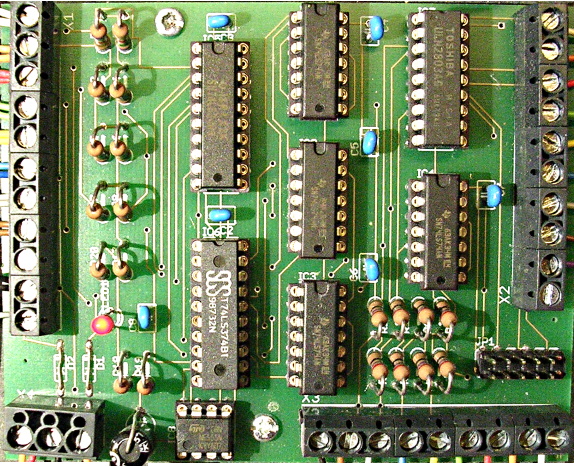

Die folgenden Bilder zeigen die gedruckte Schaltung sowie ein vollständig aufgebautes Board:

Natürlich gab es vor der gedruckten Schaltung Prototypen. Diese kann man hier (hardware_prototypen.php) „bewundern“ (folgt noch).